BRCI là gì và nguyên lý hoạt động ra sao?

Tìm hiểu Biased Resistive Contrast Imaging (BRCI) – kỹ thuật phân tích logic tĩnh không phá hủy trong IC CMOS công suất thấp. Ứng dụng, ưu nhược điểm, quy trình và khi nào nên sử dụng.

5/23/20255 phút đọc

Biased Resistive Contrast Imaging (BRCI) là gì?

Biased Resistive Contrast Imaging (BRCI) là một kỹ thuật tạo bản đồ logic của mạch tích hợp CMOS đang hoạt động ở trạng thái tĩnh, tiêu thụ dòng thấp dưới điều kiện phân cực. BRCI cho phép phân tích mà không cần loại bỏ lớp passivation, giúp bảo toàn cấu trúc ban đầu của IC. Kỹ thuật này hoạt động tương tự như Resistive Contrast Imaging (RCI), nhưng với điều kiện mạch CMOS đã được phân cực. Trong trạng thái tĩnh, các đường dẫn dẫn điện trên IC sẽ nối với VDD hoặc VSS, tạo nên sự khác biệt điện trở có thể hiển thị thành bản đồ logic.

BRCI giảm thiểu hoặc loại bỏ nhu cầu loại bỏ các lớp bề mặt như passivation hoặc lớp kim loại trên cùng khi xác định lỗi, nhờ khả năng ghi nhận dao động nhỏ trong dòng cung cấp tĩnh của IC. Tuy nhiên, kỹ thuật này phù hợp nhất với các mạch CMOS có dòng cung cấp dưới 250 µA. Khi vượt ngưỡng này, tín hiệu BRCI trở nên khó hoặc không thể phát hiện do giới hạn của thiết bị khuếch đại dòng thương mại.

Ứng dụng và giới hạn của BRCI

BRCI hoạt động hiệu quả nhất khi so sánh giữa IC lỗi và IC chuẩn (“Golden Sample”). Sự khác biệt về bản đồ logic giữa hai ảnh giúp xác định nhanh khu vực cần phân tích sâu. BRCI cũng cho phép xác định các đường dẫn có trạng thái logic sai. Sau đó, kỹ thuật backtrace được dùng để lần ngược về nguyên nhân gốc (như đứt mạch, lỗi truyền tín hiệu, v.v.).

Một ứng dụng đặc biệt khác là phát hiện conductor bị hở thông qua sự thay đổi trạng thái logic rõ rệt dọc theo đường dẫn. Với các mạng điện trở màng mỏng hoặc cấu trúc không có transistor, BRCI (hoặc RCI) là phương án thay thế khả thi khi kỹ thuật Charge-Induced Voltage Alteration (CIVA) không hoạt động hiệu quả.

BRCI nên được áp dụng khi cần phân tích logic tĩnh của các conductor nằm sâu trong IC công suất thấp, đặc biệt khi không thể loại bỏ lớp kim loại mà không ảnh hưởng đến trạng thái logic. Dù BRCI có thể coi là “không phá hủy” ở mức năng lượng thấp (<1.0 kV), nhưng vẫn có nguy cơ ảnh hưởng đến hoạt động IC nếu sử dụng năng lượng tia cao.

Phân tích ảnh BRCI và kỹ thuật trừ ảnh số

Có hai phương pháp để phân tích ảnh BRCI:

Quan sát trực tiếp: So sánh bằng mắt giữa hai ảnh BRCI. Cách này đơn giản nhưng không hiệu quả với ảnh độ phân giải cao hoặc IC phức tạp.

Phép trừ ảnh số: Chuyển ảnh sang dạng số, căn chỉnh và thực hiện trừ ảnh để làm nổi bật khác biệt logic. Phép trừ ảnh giúp loại bỏ vùng có cùng trạng thái logic, chỉ giữ lại các khác biệt rõ ràng giữa hai trạng thái logic.

Phép trừ ảnh có thể thực hiện giữa hai trạng thái logic khác nhau trên cùng một IC bị lỗi, hoặc giữa IC lỗi và IC chuẩn, với điều kiện các ảnh phải được căn chỉnh (phóng đại, xoay, nghiêng) trước khi trừ. Điều này cực kỳ hữu ích với các IC phức tạp khi việc “soi thủ công” trở nên bất khả thi.

Quy trình thực hiện BRCI hiệu quả

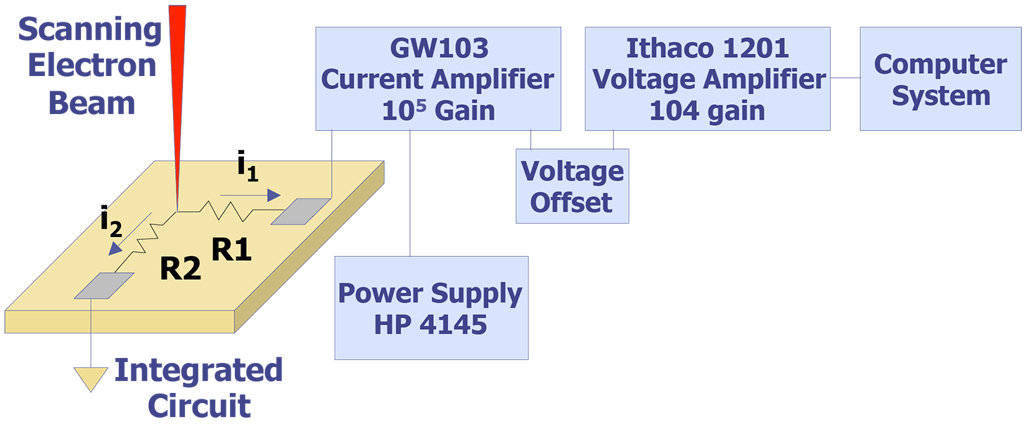

Ảnh BRCI được ghi lại khi chùm tia điện tử quét qua bề mặt IC. Tín hiệu dao động dòng sinh ra từ hiện tượng tiêm electron được khuếch đại qua hai giai đoạn để tạo ra ảnh phản ánh logic nhị phân:

Giai đoạn đầu khuếch đại dòng cung cấp và loại bỏ thành phần DC.

Giai đoạn sau khuếch đại dao động dòng điện để tạo bản đồ điện trở của các conductor.

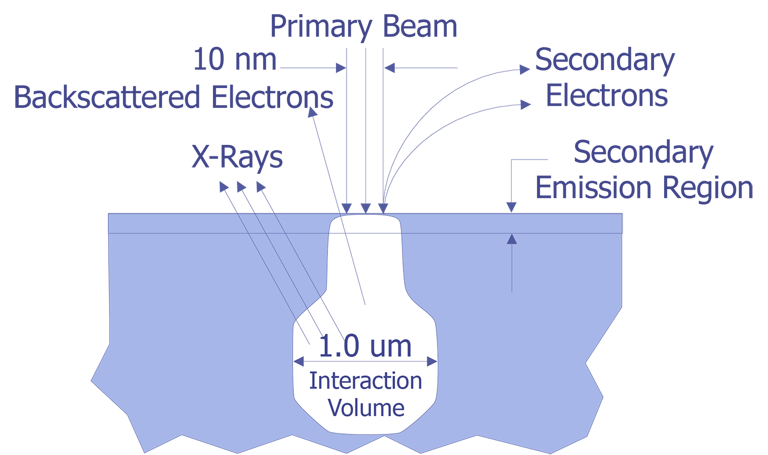

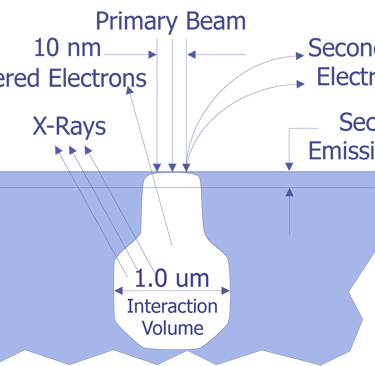

Để đạt hiệu quả tối đa, cần tăng năng lượng chùm tia điện tử đến mức vùng tương tác cắt vào các conductor cần khảo sát. Công thức thực nghiệm để tính toán năng lượng cần thiết như sau:

R = 0.022 × E^1.65

Trong đó R là độ sâu (µm), E là năng lượng chùm tia (kV). Tuy nhiên, không nên vượt quá mức cần thiết để tránh tạo tín hiệu EBIC gây nhiễu hoặc làm thay đổi điện áp ngưỡng của transistor CMOS.

References on BRCI

E.I. Cole, "A New Technique for Imaging the Logic State of Passivated Conductors: Biased Resistive Contrast Imaging", Proceedings of the IEEE International Reliability Physics Symposium (1990).

BRCI là công cụ phân tích lỗi cực kỳ hữu ích với IC CMOS công suất thấp, khi cần khảo sát trạng thái logic của các conductor dưới lớp kim loại mà không gây ảnh hưởng đến cấu trúc IC. Dù phạm vi ứng dụng của BRCI bị giới hạn, khả năng thăm dò xuyên qua lớp phủ và kim loại (như lớp kim loại 2) khiến nó trở thành công cụ phân tích giá trị trong các tình huống đặc biệt.

© Copyright - All Rights Reserved

NudgeInsepct

Liên hệ: Hồ Lê Long Thiên (Mr.)

+84 (0) 839 54 9178 info@nudgeinspect.com

VP HCM: Tòa nhà Saigon Paragon, 3 Nguyễn Lương Bằng, Tân Mỹ, Quận 7, Hồ Chí Minh